# Analytical Modeling of SON MOSFET and Realization Inverter Circuit for High Speed and Ultra Dense Low Power Circuits

Kousik Naskar\*, C.J. Clement Singh, Subir Kumar Sarkar

Department of Electronics & Telecommunication Engineering, Jadavpur University, Kolkata-700032, India

(Received 10 February 2012; published online 04 June 2012)

In the recent years, there has been considerable interest in the realization of high speed, small-size and low-power consuming devices and systems. As a consequence, the search for new principle of operation of the small-size, high speed and low-power device is becoming more and more important. In our earlier paper, it has been established that SON technology, not only improve the dc performance with reduce a short-channel effect and threshold voltage, it also improves the frequency response due to improvement in conductance and reduced parasitic effect. Further, it is already in our knowledge that SCEs are suppressed in dual material gate MOSFETs because of the perceivable step in the surface-potential profile, which screens the drain potential. The concept of dual material gate has been applied to SON MOSFETs structure and the features exhibited by resulting new SON structure has been examined for the first time by developing an analytical model and the result agree well with the MEDICI simulation values. In order to substantiate the merits of the proposed SON MOSFETs, a MOS Inverter is realized using the SON MOSFETs and its performance is investigated as an aid to the high-speed, ultra-dense and low-power circuit related work.

Keywords: SON, SOI, Dual Material Gate, MEDICI, Inverter, Short Channel Effects.

PACS numbers: 84.30. - r, 85.30.De, 85.40.Bh, 85.40.Qx,

### 1. INTRODUCTION

Continuous progress in semiconductor technology has enabled the relentless evolution of electronics, information technology and communication [1-3]. It is evident that power consumption, leakage issues, scalability and noise immunity will be the bench mark for future devices in VLSI circuit design. Since the speed of MOSFET is intrinsically limited by the carrier transit time, the most obvious approach to improve the device speed is to reduce the gate length [4-6]. When the gate length is aggressively scaled, the gate begins to lose control over the channel and the parasitic condition results in saturation, possibly in a reduction of transconductance and in an increase of drain conductance [7-10]. It has already been established that under sub 100 nm regime, conventional MOSFET scaling concepts will be confronted with physical limitations-the lattice constant of Si. The major problems of scaling down the conventional MOSFETs include: (a) quantum mechanical tunnelling through the thin gate oxide, from source to drain and from drain to body; (b) threshold voltage control induced by random doping effects; (c) short channel effects (SCE) and mobility degradation; and (d) process control of thin layer uniformity and accurate lithography and implantation. In order to extend the lifetime of the Sibased CMOS technology, devices with new structures and/or new materials need to be considered [11-15]. Several performance boosters have been proposed in the literature and the International Technology Roadmap for Semiconductor (ITRS) suggest that one or more technology boosters may be required for devices beyond the 45 nm technology node in order to sustain the increase of intrinsic device speed [16]. Continuous down scaling of bulk MOSFET produces strong short channel effects and consequently a high leakage current which limits farther miniaturization of MOSFET [17-20]. Major issue with future MOSFET is how to handle different short-channel effects [21-25]. New device structures like thin-body fully depleted Silicon-On-Insulator (SOI) and recently developed Silicon-On-Nothing (SON) MOSFET, offer advantages over the conventional transistors. In a SOI or SON MOSFET, SCEs are influenced by thin-film thickness, thin-film doping density, substrate biasing, buried oxide thickness, processing technology and material used as gate oxide layer or as BOX layer. SON is found to be more resistive against different short channel effects, more specially Drain Induced Barrier Lowering (DIBL) and two dimensional charge sharing effect modifies threshold voltage of device with small channel length. In long channel devices, gate can be considered to be completely responsible for depleting the channel, whereas in every short channel devices, a significant portion of the depletion region charge under the gate is actually due to drain and source junction depletion rather than the bulk depletion induced by the gate and this effect is known as two-dimensional charge sharing effect. Use of different dielectric materials as GOX or BOX layer, modifies the coupling effect of the lateral field and vertical field at different regions of the device and modifies its performance and which initiates the advantages of SON over SOI structure. In this paper, we have assumed our previously developed analytical models [RF] together with the dual material gate concept to realize a typical CMOS inverter circuits with SON MOSFETs and its performance is studied analytically and compared with result associated with CMOS and SOI based inverters. Power dissipation, propagation delay, dc characteristics, frequency response, are investigated. This type of combined analytical and simulation approach allows us to predicts the technology road map for future ultra-dense, lowpower nano-electronics devices and their efficiency in RF frequency range.

<sup>\*</sup> kousik\_naskar@yahoo.co.in

### 2. MODEL

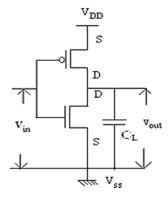

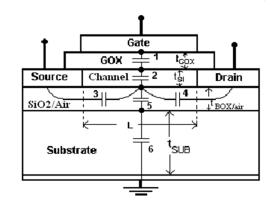

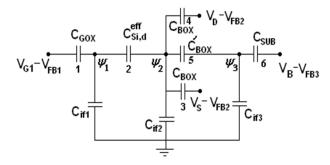

Currently there is no well-established analytical model for SON MOSFET. Hence, an analytical model is developed [5, 7] by us to estimate the essential parameters (like surface potential, electrical field, threshold voltage, DIBL etc) for SON MOSFETs they are then used to realize a inverter circuit as an aid to digital circuit related work. We tried to evaluated power dissipation, propagation delay, frequency response of SON based inverter to establish SON's superiority over SOI MOSFET's. A more realistic generalized three-interface compact capacitance threshold voltage model of SON MOSFET is developed and relevant analytical expressions are derived [4, 5, 7]. The current voltage model is developed using the derived expression and the basic charge control analysis incorporating necessary shortchannel phenomena. Analytical model is developed for SON MOSFET with an intention for using it in digital circuits to get low power VLSI chips. Analysis is limited here on SON based NOT gate (inverter) [Fig. 1] only to have a feeling of the effects of the changes of the device dimension on the power consumption, circuit speed and different threshold voltage modifying short channel phenomena like junction-induced 2D-effects. We have investigated the effect of device parameters on surface potential, threshold voltage, on and off current, sub-threshold slope and DIBL expression. The SON-MOSFET technology is found to offer devices with further scalability and enhanced performance in terms of threshold voltage rolloff, sub-threshold slope and greater current derivability thereby providing scope for further miniaturization of devices [4, 5, 7] and much better performance improvement [26]. SOI/SON-MOSFET layered structure and its equivalent capacitive model are depicted in Fig. 2 and Fig. 3, respectively [5]. In the present work, we have adopted the SON's analytical model of our previous work [7] and extended SON's merits in a digital circuit realization. The various expressions for SON-MOSFET adopted in our present analysis are presented here for individual SON and in performance analysis we have incorporated combination of both the SONs.

# 2.1 Equivalent Capacitive Model

A layered structure of a SON MOSFET is shown in Fig. 2. The structure considered here has poly silicon (n+) gate. Let  $t_{\rm GOX}$ ,  $t_{\rm Si}$ ,  $t_{\rm BOX/air}$  and  $t_{\rm sub}$  be the thickness of gate oxide, silicon channel layer, BOX layer and substrate layer respectively. L is the effective channel length of the device.

Fig. 1 - Circuit of SON based inverter

Fig. 2 - SOI/SON-MOSFET layered structure

Fig. 3 - Equivalent capacitance model

In Fig. 3  $C_{GOX}$  is the gate oxide capacitance,  $C'_{BOX}$  is the capacitance due to substrate bias and  $C_{BOX}$  is the capacitance due to fringing field,  $C_{if(1,2,3)}$  are the interface state capacitances for three interfaces,  $C_{Si,d}^{eff}$  is the silicon channel depletion capacitance.  $V_{FBI}$  is the flat band voltage at the front interface of the channel due to gate;  $V_{FB2}$  is the flat band voltage at the channel back interface due to source/drain and  $V_{FB3}$  is the flat band voltage at the back interface of the channel due to substrate.

### 2.2 Fringing Field Effect

Till now, two dimensional potential profile in BL region is quite complex to determine but capacitive model could be a possible solution to that problem [4]. Lateral field penetration from source and drain in the BOX in a fully depleted SOI/SON MOSFET is responsible for a dramatic increase of short-channel effects [30]. The coupling between channel back interface potential and the source or drain potential through burred layer can be represented by two capacitor ( $C_{BOX}$ ) [7]. Both the capacitor have identical values for low  $V_{DS}$  with horizontally symmetrical potential distribution in BL around the channel center and they can be expressed as [28].

$$C_{BOX(Drain-Channel)}(z) = \frac{K_{BOX/air}}{t_{BOX/air} \left[ \exp \left( \frac{\pi}{t_{BOX/air}} \left( z + \frac{L_{eff}}{2} \right) \right) - 1 \right]}$$

and

$$C_{BOX(Drain-Channel)}(z) = \frac{K_{air}}{t_{BOX/air} \left[ \exp \! \left( \frac{\pi}{t_{BOX/air}} \! \left( z - \frac{L_{eff}}{2} \right) \right) - 1 \right]}$$

### 2.3 Channel Lateral Field Effect

Channel effect lateral field effect due to high drain biased induced field in a short channel device can be incorporated in the threshold voltage model through a well known technique "voltage dropping transformation(VDT)" [29]. According to VDT, the effects of lateral field in the channel initiated by source and drain junctions are equivalent to a reduction in the effective channel doping [30]. Using VDT for modeling short channel effects (DIBL), the effective channel doping is given by [31]

$$N_A^* = N_A - rac{2arepsilon_{Si} V_{DS}^*}{q L_{eff}^2} \; ,$$

where  $V_{DS}^*$  is an effective voltage given by

$$\begin{split} V_{DS}^* &= V_{DS} + 2 \left( V_{bi} + \Psi_2 - \Psi_1 \right) + \\ &+ 2 \sqrt{ \left( V_{bi} + \Psi_2 - \Psi_1 \right) \left( V_{DS} + V_{bi} + \Psi_2 - \Psi_1 \right) } \end{split}$$

Here  $V_{DS}$  is the drain-source voltage,  $V_{bi} = (k_BT/q)\ln(N_AN_D/n_i^2)$  is the built in potential,  $k_B$  is Boltzman constant,  $\Psi_2$  is the bottom potential of the channel area and  $N_A$  is the silicon impurity doping concentration. Appling voltage doping transformation, the effective channel depletion layer capacitance is given as [4]

$$C_{Si,d}^{eff} = rac{dQ_d}{d\Psi} = rac{qN_A^*t_{Si}L_{eff}}{\Psi_{S1} - \Psi_{S2}}$$

Here  $Q_d$  is the total charge per unit area of silicon channel.

In a short channel device, threshold voltage is a function of drain bias or channel potential. V(x) threshold voltage expression can be written as

$$\begin{split} V_{th} &= V_{FB1} + H \left[ 1 + \frac{2C_{BOX} \left\{ \frac{C - FV(x)}{G} \right\}}{C_{GOX} \left\{ \frac{C - FV(x)}{G} + 2C_{BOX} \right\}} \right] - \\ &\left( V(x) - 2V_{FB2} \right) \frac{\left\{ \frac{C - FV(x)}{G} \right\} C_{BOX}}{C_{GOX} \left\{ \frac{FV(x)}{G} + 2C_{BOX} \right\}} \\ &I_{on} &= WC_{G(eff)}(V_{DD} - V_t) v_s, \end{split}$$

$$I_{off} = I_0 \ 10 - (V_{n(low)} - \Delta V_{n(DIBL)}).$$

where  $I_{on}$  = "on state current".  $I_{off}$  = "off state current".  $V_{t(low)}$  is average current velocity at low  $V_{DS}$  and  $\Delta V_{n(DIBL)}$  is  $V_t$  reduction.

Subs threshold slope:

$$S \cong (600mV)1 + \frac{\varepsilon_{si}(1-x)G_{ex}}{\varepsilon_{ox}} \cdot \frac{t_{ox}}{td}$$

where

$$t_{d} = Depletion \ width = \sqrt{\left(2\varepsilon_{si}\frac{\psi_{s}}{eN_{si}}\right)}$$

$$DIBL \cong \frac{3t_{d}t_{ox}V_{ds}}{Leff 2\bigg(1 + \frac{\varepsilon_{si}}{\varepsilon_{ox}}\frac{t_{ox}}{t_{d}}\bigg)} \; ,$$

$V_s$  = average current velocity near the source, "W" is the width,  $\varepsilon_{ox}$  and  $t_{ox}$  are gate oxide permittivity and thickness, respectively. All the symbols have the usual significance as [5].

### 2.4 Propagation delay

In our analysis, we will calculate the propagation delay of an Inverter. Looking at the high-to-low transition for  $V_{out}$  for the inverter, we follow the trajectory of the nMOS current-voltage transistor characteristic.

The load capacitance  $C_L$  consists of two major components.

- 1. The total gate capacitance  $C_G$  that is the gate capacitance of the transistors being driven by the inverter.

- **2.** A parasitic capacitance  $C_P$  that results from the drain diffusions of the driving inverter and the wiring to the gates being driven.

We add the values of  $C_G$  and  $C_P$  to obtain the total load capacitance  $C_L$ . Substituting  $C_G + C_P$  for  $C_L$ , we find the value of  $t_{PHL}$  to be and  $t_{PLH}$  also [32]

$$t_{PHL} = \frac{(C_G + C_P)V_{OH} / 2}{k_n / 2(V_{DD} - V_{Th})^2} , \quad t_{PLH} = \frac{(C_G + C_P)V_{OH} / 2}{k_p / 2(V_{DD} - V_{Tp})^2}$$

The average propagation delay  $t_P$  can be estimated by averaging the transition times as shown in

$$t_p = (t_{PHL} + t_{PLH})/2.$$

### 2.5 Power dissipation

In an Inverter, power dissipation has three component: like Dynamic power dissipation, short circuit power dissipation and static power dissipation (leakage and sub-threshold leakage). When the inverter is in either of its stable state (ON or OFF) there is only static power dissipation which is contributes less than 20 % of the total power dissipation of the inverter [33]. The dynamic power dissipation (which is the most significant contributor of power dissipation) occur during change of state (OFF to ON or ON to OFF). The short circuit power dissipation is not directly related to Inverter, rather it occurs due to non ideal input or output signal with finite noise and fall times [32]. Hence we have incorporated in our calculation dynamic and static dissipation only and ignored the short circuit power dissipation [34-36].

Where Dynamic power dissipation:

$$\begin{split} P_{dn} &= \frac{1}{T} \Bigg[ \int\limits_{0}^{T/2} V_{out} \bigg( -C_{LOAD} \, \frac{dV_{out}}{dt} \bigg) dt + \\ &+ \int\limits_{T/2}^{T} \big( V_{dd} - V_{out} \big) \bigg( C_{LOAD} \frac{dV_{out}}{dt} \bigg) dt \Bigg]. \end{split}$$

Static power or leakage power:

$$p_{lkg} = V_{dd}k_{\rm B} \exp \left[ \frac{(V_{gs} - V_t)q}{nk_{\rm B}T} \right] \left[ 1 - \exp \left( \frac{V_{ds}q}{k_{\rm B}T} \right) \right]. \label{eq:plkg}$$

### 3. RESULT AND DISCUSSION

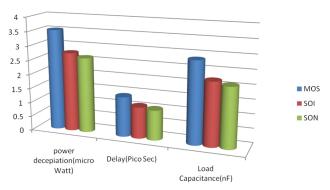

To study the advantages of SON device in a SOI and CMOS logic circuit, SON based inverter circuit is studied by developing the analytical model of SON device. In the present work, the effectiveness of dual material gate has been applied to the SON MOSFET structure and the features shown by the proposed structure have been examined by the first time developing a 2D analytical model and it is exhibited that the result obtained form the proposed model agree well with the MEDICI simulation results. It also emphasized that the proposed structure leads to reduced SCEs, as the surface potential profile shows a step at the interface of the two metal which reduced drain conductance are DIBL. The power consumption of SON based inverter is found to be 5.26 % lower than SOI based inverter and 34.08 % lower than COMS inverter. the signal transmission time is 5.27 % lesser than SOI based inverter and 34.20 % less than CMOS. Load capacitance is the least for SON based inverter among the three similar inverter circuits.

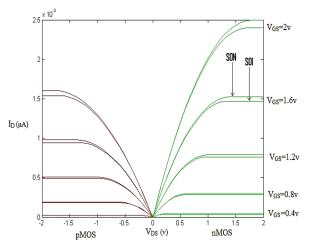

**Fig.** 4 –  $I_D$ - $V_{DS}$  Curve for the inverter

Fig. 4 represents the  $I_D$ - $V_{DS}$  characteristics of SON MOSFETs based on ours calculations and SOI MOSFETs at room temperature for a gate voltage range 0 to 2 volt. A significant drain current enhancement in SON MOSFETs is observed compared to bulk MOSFETs is observed which affects the circuit efficiency in CMOS logic techniques.

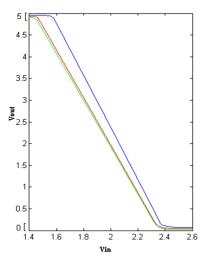

The switching Characteristics for a SON bassed inverter (Fig. 1) are depicted in Fig. 5. It appears that SON based inverter is faster than CMOS inverter and SOI inverter.

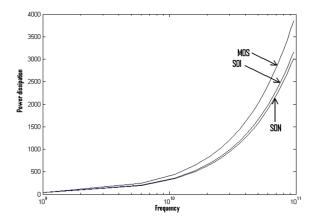

Fig. 6 shows the variation of power dissipation with frequency of the input signal. It appears that the power dissipation is lower for SON based inverter compared to CMOS inverter and SOI inverter. In order to establish the performance supremacy of the present SON based inverter a Table 1 is provided depicting various parameters. Typical parameters used for such performance comparison are: W = 1 micro meter,  $L_z = 120$  nano meter,  $C_{gox} = 44.45$  aF.

Similarly a Bar chart is also given in Fig. 7 to visualize the performance variation of difficult devices and inverter based on those devices.

Fig. 5 – Simulates the switching characteristics for the SON-based inverter

Fig. 6 - Frequency response of inverters

${\bf Fig.~7}-{\bf Bar~chart~showing~power~dissipation~and~Propagation~Delay~for~Various~types~of~inverter$

Table 1 – Calculated /simulated parameters for inverter with different device structure scheme

| Device | Threshold | Power de-         | Propa-     | Load capaci-           |

|--------|-----------|-------------------|------------|------------------------|

|        | Voltage   | capita-tion       | gation     | tance                  |

|        | (v)       | $10~\mathrm{Ghz}$ | delay      | (ff)                   |

|        |           | frequency         | (pico sec) |                        |

|        |           | (micro watt)      |            |                        |

| MOS    | 0.2503    | 140.91            | 3.535      | $2.865 \times 10^{-9}$ |

| SOI    | 0.1926    | 110.62            | 2.773      | $2.219 \times 10^{-9}$ |

| SON    | 0.1848    | 105.09            | 2.634      | $2.104 \times 10^{-9}$ |

**Table 2** – Power dissipation and propagation delay of inverter for various device parameter

| Device |       | Na = 1 -            | Lz = 50 -            | Tgox =                   | Tsi = 30 -          |

|--------|-------|---------------------|----------------------|--------------------------|---------------------|

|        |       | $10 \times 10^{21}$ | $330 \times 10^{-9}$ | $5 - 8.5 \times 10^{-9}$ | $90 \times 10^{-9}$ |

|        |       |                     |                      |                          |                     |

| MOS    | Power | 596.61 -            | 758.81 -             | 264.14 -                 | 610.24 -            |

|        | (mW)  | 600.19              | 728.12               | 266.33                   | 614.13              |

|        | Delay | 2.213 -             | 2.665 -              | 0.984 -                  | 2.303 -             |

|        | (pS)  | 2.200               | 2777                 | 0.976                    | 2.288               |

| SOI    | Power | 492.13 -            | 592.01 -             | 267.83 -                 | 480.60 -            |

|        | (mW)  | 494.63              | 570.64               | 269.53                   | 482.93              |

|        | Delay | 1.761 -             | 1.990 -              | 0.955 -                  | 1.731 -             |

|        | (pS)  | 1.752               | 2.065                | 0.949                    | 1.722               |

| SON    | Power | 469.78 -            | 592.45 -             | 265.11 -                 | 478.09 -            |

|        | (mW)  | 471.92              | 574.15               | 268.04                   | 480.81              |

|        | Delay | 1.670 -             | 2.019 -              | 0.938 -                  | 1.714 -             |

|        | (pS)  | 1.662               | 2.084                | 0.928                    | 1.704               |

|        |       |                     |                      |                          |                     |

# 4. CONCLUSION

In the present work we have used our analytical model for SON MOSFET and shown its supremacy over other device like SOI and CMOS devices. We have employed over SON model to realize an inverter and studied

### REFERENCES

- 1. Y.-B. Kim, *TEEM* 11, 93 (2010).

- J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits: A Design Perspective, Second Edition, (Prentice Hall 1996)

- 3. J. Pretet, S. Monfray, S. Cristoloveanu, T. Skotnicki, *IEEE T. Electr. Dev.* **51**, 240 (2004).

- Subir Kumar Sarkar, Sanjoy Deb, N. Basanta Singh, Debraj Das, *Mater. Sci.: An Indian Journal* 7, Issue 1 (2011).

- Sanjoy Deb, N. Basanta Singh, Debraj Das, A.K. De, Subir Kumar Sarkar, Int. J. Electron. 98, 1465 (2011).

- K. Roy, S. Mukhopadhyay, H. Mahmoodi-Meimand, P. IEEE 91, 305 (2003).

- Saptarsi Ghosh, Khomdram Jolson Singh, Sanjay Deb, Subir Kumar Sarkar, J. Nano- Electron. Phys. 3 No 1, 569 (2011).

- K. Roy, S.C. Prasad, Low-Power CMOS VLSI Circuit Design (New York: Wiley: 2000).

- A. Nabavi-Lishi, N.C. Rumin, *IEEE T. Comput. Aid. D.* 13, 1271 (1994).

- Sanjoy Deb, N. Basanta Singh, Subir Kumar Sarkar, Expert Syst. Appl. 38, 12999 (2011).

- S. Dutta, S.S.M. Shetti, S.L. Lusky, *IEEE J. Solid-St. Circ.* 30, 864 (1995).

- T. Sakurai, A.R. Newton, *IEEE J. Solid-St. Circ.* 25, 584 (1990).

- 13. G. Timp and et al., *Electron Devices Meeting*, 55 (IEDM Technical Digest. International, 1999)

- 14. K.O. Jeppson, *IEEE J. Solid-St. Circ.* 29, 646 (1994).

- M. Shoji, CMOS Digital Circuit Technology, Chapters 2 (Prentice Hall: 1988).

- M. Trabelsi, L. Militaru, N. Sghaier, A. Savio, S. Monfray, A. Souifi, *IEEE T. Nanotechnol.* 10, 402 (2011).

- 17. J.L. Rossello, J. Segura, *IEEE T. Circuits-I* **51**, 1301 (2004).

- A. Nabavi-Lishi, N.C. Rumin, *IEEE Trans. Comput. Aid.* D. 13, 1271 (1994).

- H. Kawaura, T. Sakamoto, T. Baba, Y. Ochiai, J. Fujita, J. Sone, *IEEE T. Electr. Dev.* 47, 856 (2000).

**Table 3** – Comparative study of dissipation, delay, capacitance respected to SON based inverter

| Device | Power Dissipa-<br>tion (Micro | Propagation<br>Delay (pico | Load Capaci-<br>tance (nF) |

|--------|-------------------------------|----------------------------|----------------------------|

|        | Watt)                         | sec)                       | ,                          |

| SON    | 105.09                        | 2.634                      | $2.104 \times 10^{-9}$     |

| SOI    | 5.26 % More                   | 5.27 % More                | 5.46 % More                |

|        | than SON                      | than SON                   | than SON                   |

| MOS    | 34.08 %                       | 34.20 % More               | 36.16 %                    |

|        | More than                     | than SON                   | More than SON              |

|        | SON                           |                            |                            |

its performance with SOI/CMOS inverter. The impact of reduced SCEs on the performance of 120 nm SON MOSFETs circuits is investigated here using the developed analytical model of SON MOSFETs devices. Significant enhancement in the circuit performance is predicted for SON based circuit thereby offering more advantages for low power VLSI circuit.

### ACKNOWLEDGEMENT

Dr. Subir Kumar Sarkar Sarkar thankfully acknowledges for financial support obtained form SON DRDO.

- J. Pretet, S. Monfray, S. Cristoloveanu, T. Skotnicki, *IEEE T. Electr. Dev.* 51, 240 (2004).

- P. K. Sahu, A. K. Biswas, C. K. Int. J. of Information and computing Science 7 No1, 54 (2004\_.

- T. Ernst, C. Tinella, C. Raynaud, S. Cristoloveanu, Solid State Electron. 46,373 (2002).

- 23. A. Ploßl, G. Krauter, Solid State Electron. 44, 775 (2000).

- K. Senthil Kumar, Saptarsi Ghosh, Anup Sarkar, S. Bhattacharya, Subir Kumar Sarkar, Appl. Mech. Mater. 110-116, 5150 (2011).

- 25. Sanjoy Deb, N Basanta Singh, Rohan Mukherjee, Subir Kumar Sarkar "A Simple Compact Analytical Model For Performance Analysis Of SON MOSFET" World Journal of Condensed Matter Physics, Scientific Research.

- T. Skotnicki, G. Merckel, T. Pedron, *IEEE T. Electr. Dev. Let.* 9, 109 (1988).

- K. Brennan, A. Brown, Theory of modern electronic semiconductor devices, (New York: John Wiley & Sons Inc.: 2002).

- 28. T. Ernst, S. Cristoloveanu, *Proc. IEEE Int. SOI Conf.*, 38 (1999).

- M.-Ch. Hu; Sh.-L. Jang, *IEEE T. Electr. Dev.* 45, 797 (1998).

- 30. K.K. Young, IEEE T. Electr. Dev. 36, 399 (1989).

- Z.-H. Liu, C. Hu, J.-H. Huang, T.-Y. Chan, M.-C. Jeng,

P.K. Ko, Y.C. Cheng, *IEEE T. Electr. Dev.* 40, 86 (1993).

- 32. Rabay, Digital intrigated circuit. Chapter 5, Page 144 Monday, September 6, 1999.

- 33. CMOS Power Consumption and Cpd Calculation (Texas Instruments Inc.; 1997).

- Th. Schulz, Ch. Pacha, L. Risch, *IEEE International SOI Conference*, 176 (2002).

- A.B. Bhattacharyya, Shrutin Ulman, International Conference on VLSI Design, 207 (VLSID/ASP-DAC: Bangalore: India: 2002).

- 36. Zhangcai Huang, A. Kurokawa, M. Hashimoto, Y. Inoue, *IEEE T. Comput. Aid. D.* 29, 250 (2010).