# Surface Passivation of Germanium Using NH<sub>3</sub> Ambient in RTP for High Mobility MOS Structure

Anil G. Khairnar, Y.S. Mhaisagar, A.M. Mahajan\*

Department of Electronics, North Maharashtra University Jalgaon 425001, Maharashtra, India

(Received 15 February 2013; revised manuscript received 30 April 2013; published online 04 May 2013)

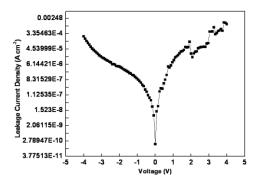

Ge CMOS is very striking for the post Si-CMOS technology. However, we have to attempt a number of challenges with regard to materials and their interface control. In this paper we have investigated the control of the interfacial properties of  $SiO_2$  / Ge gate stack structures by the thermal nitridation technique. Structural and electrical properties of  $SiO_2$  gate-dielectric metal-oxide-semiconductor (MOS) capacitors deposited by sputtering on germanium are studied. The structural characterization confirmed that the thin film was free of physical defects and smooth surface of the films after PDA at  $500~^{\circ}$ C in  $N_2$  ambient. The smooth surface  $SiO_2$  thin films were used for Pt /  $SiO_2$ / GeON / Ge MOS structures fabrication. The MOS structure yields a low leakage current density of  $9.16 \times 10^{-6}$ A·cm $^{-2}$  at 1 V.

Keywords: Germanium, Passivation, SiO2, RF-Sputtering, Leakage current

PACS numbers: 77.55. + f, 81.20.Fw, 68.37, Hk, 85.30.Tv, 84.37. + q

## 1. INTRODUCTION

As the constant scaling of Si metal-oxidesemiconductor (MOS) devices approaching its primary limits, a variety of modified channel materials, such as a strained Si, are being considered to increase the drain current by improving the carrier mobility in the channel region. An alternative approach is to continue the trend of scaling by implementing novel channel materials with better transport properties than silicon. Among the studied materials the carbon nanotubes, silicon nanowires, graphene, Ge and III-V compound semiconductors such as InSb and InGaAs which have significantly higher intrinsic (p or n) mobility than silicon[1-4]. Germanium is being considered as a potential channel material for the next generation MOS devices due to its much higher low field electron (two times higher) and hole (four times higher) mobilities than Si [5-6]. One of the serious issues in establishing Ge-based CMOS technology has been the effective passivation of Ge surfaces by dielectrics with better interface properties [7-8]. The establishment of fabrication technology for high-performance Ge gate stack structures is required for future Ge MOS devices. Different passivation techniques have been employed to form the stable surface over the Ge to get the superior interface properties such as nitridation, sulfur passivation, Si passivation etc [9-10]. In this work we have performed the thermal nitridation of Ge in NH<sub>3</sub> ambient using RTP system for the passivation of germanium surface [11]. Since SiO<sub>2</sub> has proven to be best insulator for the success of Si semiconductor technology since last few decades [12]. SiO<sub>2</sub> has high band gap (9 eV), high dielectric strength of 10<sup>7</sup> V/cm, compatibility with polysilicon gate process, excellent thermal stability with silicon, low density of interface states and good electrical reliability [13]. In this work the deposited SiO<sub>2</sub> is used as gate dielectric over the surface passivated germanium for the fabrication of Ge/GeON/SiO2 gate stack. RF sputtering is physical vapor deposition (PVD)

based technique combined with plasma offers a low temperature processing and blocks the oxygen from the ambience, which prevents the formation of interfacial layer (IL). Hence, good quality of gate dielectric thin films can be achieved using RF-Sputtering technique which is important in the fabrication of CMOS devices [14].

In this study, the surface properties of  $SiO_2$  films on Ge substrates with special attention on the leakage current in MOS capacitors is investigated after Ge passivation using rapid thermal nitridation in NH $_3$ . Second section of the paper describes the experimental details, third section includes the results and discussion part and fourth section concludes the paper.

## 2. EXPERIMENTAL DETAILS

Germanium substrates with resistivity of 0.01- $0.1 \Omega$ cm were used for deposition of SiO<sub>2</sub> thin films. The 2" p-type Ge (100) substrates were cleaned using cyclic HF DI rinse. The substrates were rinsed in 2 % HF and de-ionized water alternately for several times, followed by blowing dry with N2. Following that, annealing in a NH3 ambient was performed inside a RTP chamber at a constant temperature of 550 °C for four minutes. Substrates were then transferred to the sputtering chamber for the deposition of SiO<sub>2</sub> thin films. The process parameters like base pressure, operating pressure, sputtering distance, sputtering time for the deposition of  $SiO_2$  were set as  $4.0 \times 10^{-5}$  mbar, 0.022 mbar, 13.5 cm and 11 minute respectively at room temperature using the Argon plasma. Post deposition annealing (PDA) was performed in N<sub>2</sub> ambient at 500 °C for 60 s under atmospheric pressure using rapid thermal annealing. To study the leakage current behavior Platinum metal was deposited as top electrode on SiO<sub>2</sub> thin films through shadow mask with electrode area of  $12.56 \times 10^{-4}$ cm<sup>2</sup> by using metal sputtering system (Nordiko) at base pressure of  $2.3 \times 10^{-5}$  mbar where substrate was kept at room temperature. The

\_

<sup>\*</sup> ammahajan@nmu.ac.in

native oxide was removed by the Buffered Hydrofluoric Acid (BHF) followed by rinsed in deionized water before the back contact formation. An ohmic contact was formed on backside of Ge substrate to form MOS capacitors by thermally evaporating the Al metal. These fabricated Pt/SiO<sub>2</sub>/GeON/Ge MOS capacitors were post metallization annealed (PMA) at 450 °C for 20 min using forming gas (90 % N<sub>2</sub>, 10 % H<sub>2</sub>) ambient. The structural characterization of annealed SiO<sub>2</sub> films was carried out by using the ellipsometer (Philips SD 1000), XRD (BRUKER Model D8 ADVANCE) and AFM. Current as function of voltage, I-V (semiconductor characterization system 4200) measurements of fabricated MOS structures were performed to study the electrical properties.

## 3. RESULTS AND DISCUSSION

#### 3.1 SEM / AFM

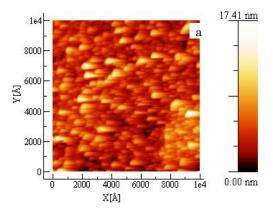

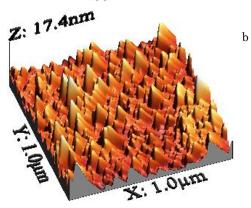

Fig. 1 shows the typical surface morphology of  $SiO_2$  thin film annealed at 500 °C examined by SEM. It is observed that samples do not reveal any physical defects such as cracks and void under the investigated magnification from low (20 k×) to high (75 k×). Two and three dimensional (2 and 3D) surface topographies

Fig. 1 – A typical SEM micrograph of  $\rm SiO_2$  film deposited on surface passivated Ge and PDA at 500  $^{\circ} \rm C$

of the investigated SiO<sub>2</sub> thin film were examined using AFM with a scanning area of  $1\times 1\,\mu m$  shown in Fig. 2a and b. The topography of the sample annealed at a 500 °C temperature was smooth and the root-mean-square (RMS) surface roughness for the deposited films was found to be 2.15 nm. 2D image showed the uniform, homogeneous distribution of the grains over entire film. 3D image revealed pyramid like nanostructure with almost uniform height.

## 3.2 Ellipsometer

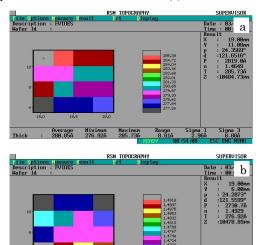

The thickness and refractive index (RI) measurement was done using Philips SD 1000 ellipsometer in raster scan method at 16 different points on the film surface at wavelength of 632.8 nm. Thickness of the GeON /  $\mathrm{SiO}_2$  bilayer dielectric stack was measured to be in the range of 27.69-28.57 nm. The thickness of interfacial GeON layer was approximately 5.52-5.79 nm. The refractive index value for dielectric stack was found to be in the range of 1.46-1.49. The measured RI value of dielectric stack is close to the RI value of  $\mathrm{SiO}_2$ . The thickness and RI topographies are shown in Fig. 3a and b respectively, the measurement

Fig. 2 – Two-dimensional AFM topography of  $SiO_2$  film deposited on surface passivated Ge and PDA at 500 °C (a). Three-dimensional AFM topography of  $SiO_2$  film deposited on surface passivated Ge and PDA at 500 °C (b)

**Fig. 3** – Thickness topography of  $SiO_2$  film deposited on surface passivated Ge and PDA at  $500~^{\circ}C$  (a). Refractive index topography of  $SiO_2$  film deposited on surface passivated Ge and PDA at  $500~^{\circ}C$  (b)

shows good uniformity of the film with excellent coverage as confirmed through AFM and SEM results.

#### 3.3 XRD

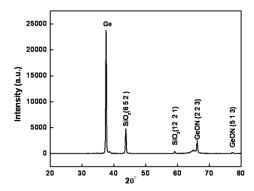

XRD measurement of  $SiO_2$  films after annealing at 500 °C temperature was carried out to examine the crys-

tal structure of SiO<sub>2</sub> films deposited on germanium. It was found that there was tetragonal (t) phase in our SiO<sub>2</sub> films with two orientations of the SiO<sub>2</sub> thin film at (6 5 2), (12 2 1) planes were observed. The diffraction planes are well matched with ICDD file number 00-089-1688, which is associated with the SiO<sub>2</sub> phase as shown in Fig. 4. In the XRD spectra the dominant peak observed at 37.55° ( $2\theta$ ) corresponds to the germanium substrate. Besides that, two additional peaks identified as germanium oxide nitride with an ICDD file number of 00-026-0685 oriented at (2 2 3) (5 1 3) is detected along with the aforementioned three peaks corresponding to nitride interfacial layer.

## 3.4 Current-Voltage Measurement

Leakage current behavior of the fabricated MOS structure is verified using the I-V measurement. The leakage current density characteristics of the investigated samples post metallization annealed (PMA) at 450 °C temperature is shown in Fig. 5. The leakage current density of devices with 500 °C annealed SiO<sub>2</sub> film is  $9.16\times10^{-6}\,\mathrm{A\cdot cm^{-2}}$  at  $1.0\,\mathrm{V}$ , which is slightly lower than the leakage current density, previously reported by Xue-Fei Li et al for HfO<sub>2</sub>/SiO<sub>2</sub> gate stack on Ge substrates [15] and by us for HfO<sub>2</sub> grown by RF sputtering technique on silicon substrates [16].

Fig. 4 – XRD spectra of  $\rm SiO_2$  film deposited on surface passivated Ge and PDA at 500  $^{\circ}\mathrm{C}$

## REFERENCES

- C. Riedl, C. Coletti, U. Starke, J. Phys. D: Appl. Phys. 43, 374009 (2010).

- Ali Javey, Hyoungsub Kim, Markus Brink, Qian Wang, Ant Ural, Jing Guo, Paul Mcintyre, Paul Mceuen, Mark Lundstrom, Hongjie Dai, Nature Mater. 1, 241 (2002)

- P. Ye, J. Gu, Y.Q. Wu, M. Xu, Y. Xuan, T. Shen, A.T. Neal, *ECS Transactions* 28 No 2, 51 (2010).

- H.C. Lin, P.D. Ye, G.D. Wilk, Solid-State Electron. 50, 1012 (2006).

- Serge Oktyabrsky, Peide D. Ye, Fundamentals of III-V Semiconductor MOSFETs (Springer: 2010).

- B.G. Streetman, S. Banerjee, Solid-State Electronic Devices, Sixth Edition (Pearson Education: 2006).

- D.P. Brunco et al, J. Electrochem. Soc. 155 No 7, H552 (2008).

- 8. Akira Toriumi, Toshiyuki Tabata, Choong Hyun Lee, Tomonori Nishimura, Koji Kita, Kosuke Nagashio,

$\bf Fig.~5-\rm J\text{-}V$  characteristics of Pt / SiO<sub>2</sub> / GeON / Ge MOS capacitor PMA at 450 °C

#### 4. CONCLUSIONS

In summary, the Ge surface has been effectively passivated by NH $_3$  annealing in RTP system. The physical and electrical properties of RF sputtered SiO $_2$ / Ge MOS capacitors have been investigated. It is found that GeON is formed during surface nitridation (NH $_3$  annealing) of germanium. SiO $_2$  films deposited on nitrided germanium are observed to be smooth surfaced and crack free. Ellipsometer and AFM confirmed the uniformity of the film. In addition, the electrical characteristics of SiO $_2$  Ge MOS capacitors showed that surface nitridation is very effective to improve the leakage current density. This concludes that the fabricated MOS structures can be useful for high mobility devices due to high mobility of carriers in germanium.

# ACKNOWLEDGMENT

Authors are thankful to CEN, IITB for providing necessary fabrication and characterization facilities under INUP scheme. One of the author A. G. Khairnar is thankful to CSIR New Delhi, India for providing senior research fellowship for carrying out this work (vide File No. 09/728(0029)/2012-EMR-I).

- Microelectron. Eng. 86, 1571 (2009).

- Qi Xie, Shaoren Deng, Marc Schaekers, Dennis Lin, Matty Caymax, Annelies Delabie, Xin-Ping Qu, Yu-Long Jiang, Davy Deduytsche, Christophe Detavernier, Semicond. Sci. Technol. 27, 074012 (2012).

- 10. S. Sioncke et al, ECS Transactions 45 No 4, 97 (2012).

- 11. Nan Wu et al, Appl. Phys. Lett. 84, 3741 (2004).

- Chun Zhao, C.Z. Zhao, M. Werner, S. Taylor, P.R. Chalker, ISRN Nanotechnology 2012, 689023 (2012).

- 13. John Robertson, Rep. Prog. Phys. 69, 327 (2006).

- A.G. Khairnar, A.M. Mahajan, Solid State Sci. 15, 24 (2013).

- Xue-Fei Li, Xiao-Jie Liu, Ying-Ying Fu, Ai-Dong Li, Wen-Qi Zhang, Hui Li, Di Wu, J. Vac. Sci. Technol. B 30, 010602 (2012).

- P.M. Tirmali, A.G. Khairnar, B.N. Joshi, A.M. Mahajan, Solid-State Electron. 62, 44 (2011).